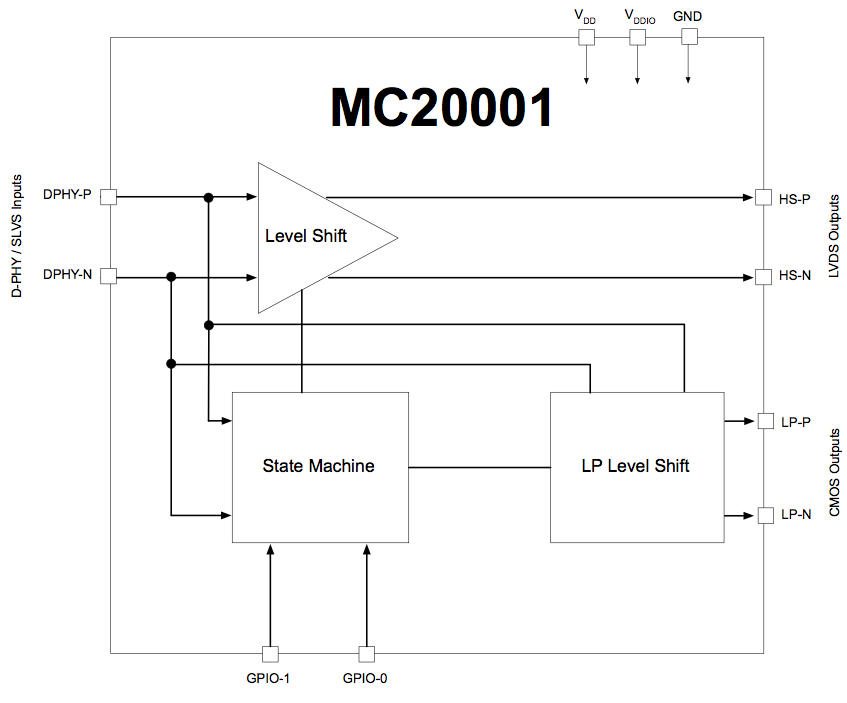

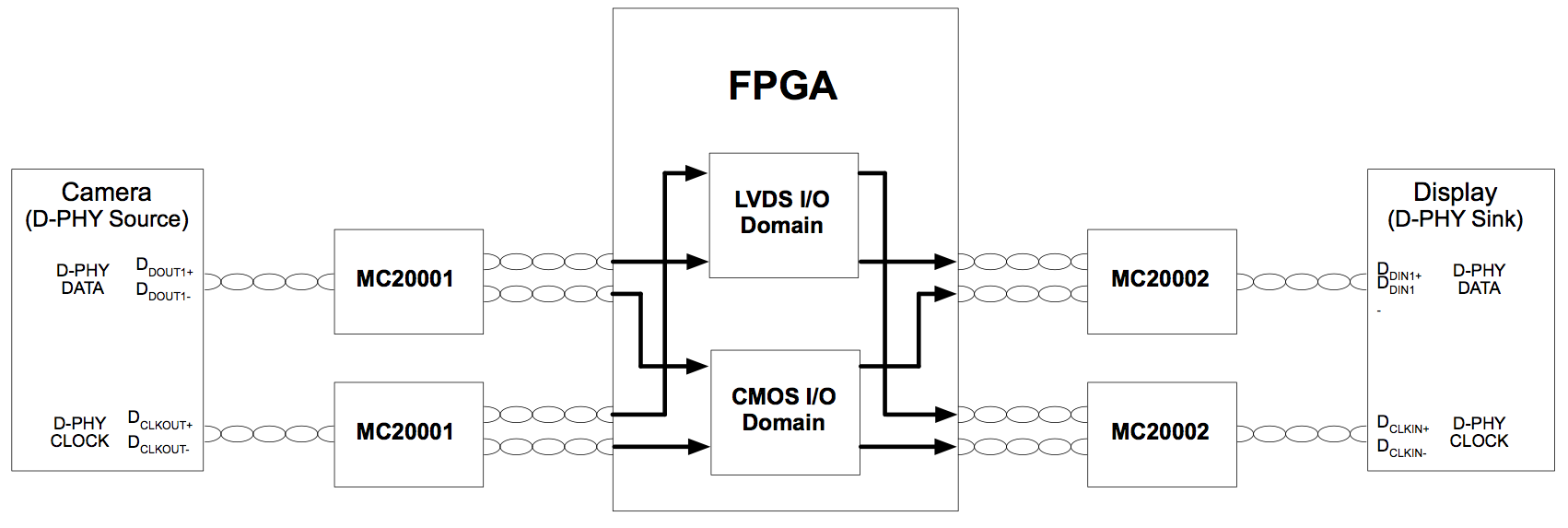

The MC20001 is a high performance FPGA bridge IC, which converts a

single MIPI D-PHY compliant input stream into LVDS high speed and CMOS

low speed output data streams.

The MC20001 can also convert an SLVS signal into an LVDS signal.

The MC20001 outputs can be directly connected to FPGAs or DSPs.

Data rates can be from 0 Mbps to 2.5 Gbps in HS (High Speed) mode and up to 20 Mbps in LPDT (Low Power Data Transmission) mode.

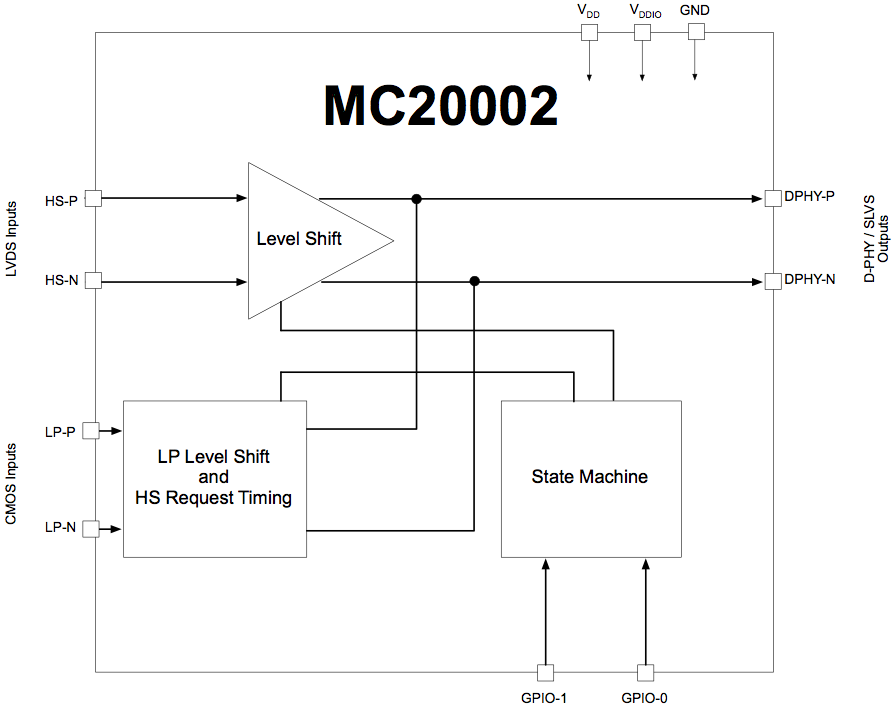

The MC20002 is a high performance FPGA bridge IC that converts incoming

LVDS high speed and incoming CMOS low speed data streams into a single

lane MIPI D-PHY compliant output stream. The MC20002 can also convert a

LVDS signal into a SLVS signal.

The MC20002 can be connected to any signal source, for example FPGAs or DSPs.

Data rates can be from 0 Mbps to 2.5 Gbps in HS (High Speed) mode and up to 20 Mbps in LPDT (Low Power Data Transmission) mode.

In MIPI D-PHY mode the THS-PREPARE timing can be controlled by the host device.

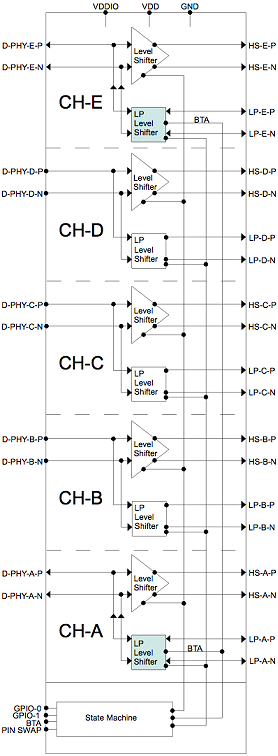

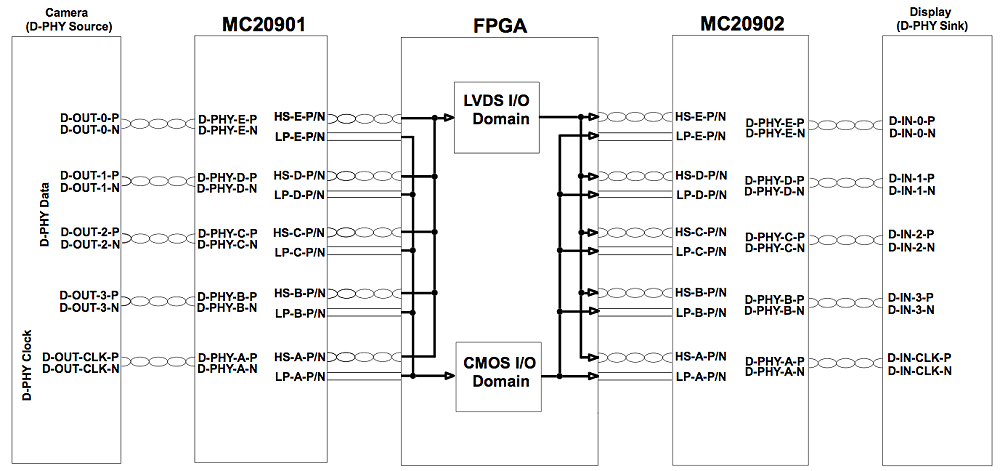

The MC20901 is a high performance 5 channel FPGA bridge IC, which

converts up to 5 MIPI D-PHY compliant input streams into LVDS high

speed and CMOS low speed output data streams.

The MC20901 can also convert SLVS signals into LVDS signals.

The MC20901 outputs can be directly connected to FPGAs or DSPs.

Data rates range from 0 Mbps to 2.5 Gbps in HS (High Speed) mode and up to 20 Mbps in LPDT (Low Power Data Transmission) mode.

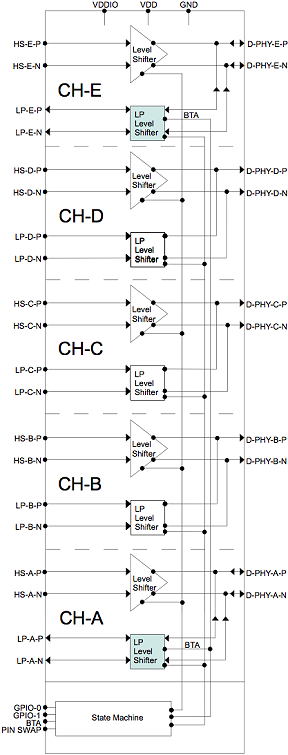

The MC20902 is a high performance 5 channel FPGA bridge IC, which converts incoming LVDS high speed and incoming CMOS low speed data streams into 5 channels MIPI D-PHY compliant output streams.

The MC20902 can also convert an LVDS signal into an SLVS signal.

The MC20902 can be connected to any signal source, for example FPGAs or DSPs.

Data rates can be from 0 Mbps to 2.5 Gbps in HS (High Speed) mode and up to 20 Mbps in LPDT (Low Power Data Transmission) mode.

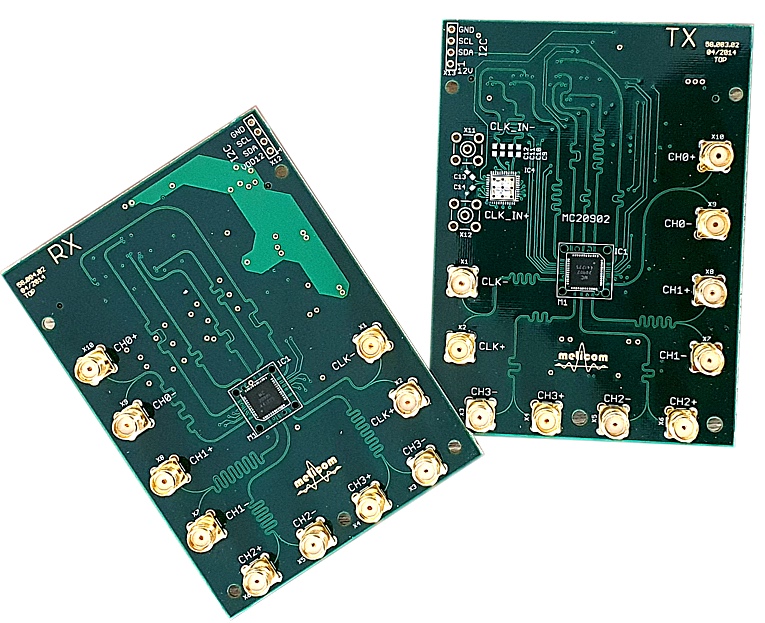

For the evaluation of its different ICs, Meticom provides MIPI master transmitter and MIPI slave receiver evaluation boards.

The evaluation boards are based on FPGA Mezzanine Cards (FMC).

These MIPI FMC connectivity mezzanine cards provide either an FMC (LPC) connector input to 4-lane/1-clock D-PHY DSI output or

a 4-lane/1-clock D-PHY CSI input to FMC (LPC) connector output.

Board schematics, design files and a bill of materials are available

See Youtube video